Articles with tag 'RISC-V'

Codethink investigates big-endian support on little-endian architectures by exploring RISC-V's new runtime-controllable endianness, with QEMU as testing base.

A summary of a Codethink sponsored project which implements a cryptographically secure bootloader, written in Rust, for RISC-V.

Codethink recently presented at the 2024 RISC-V Summit Europe. Learn about our experiences at the event and our work on RISC-V.

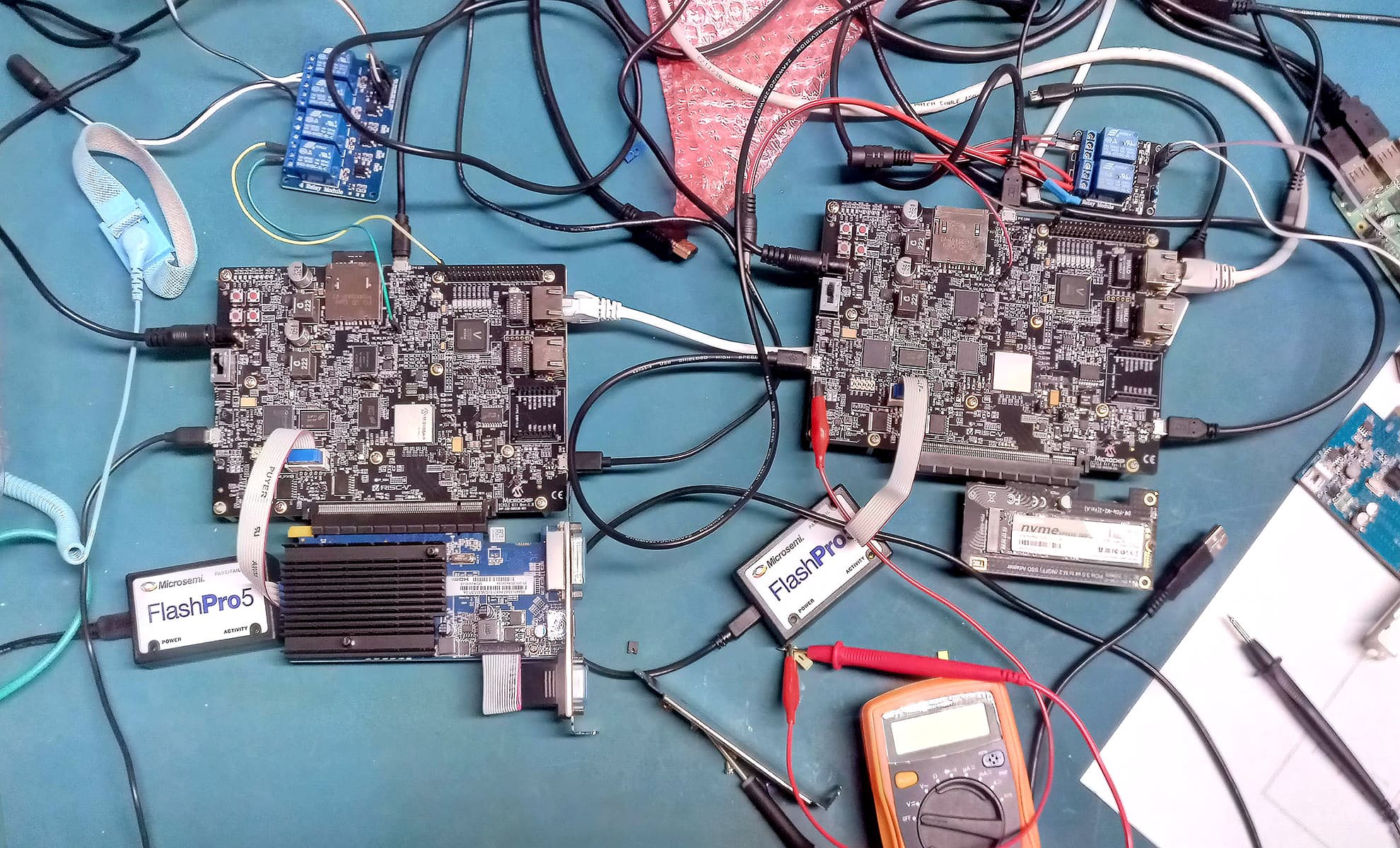

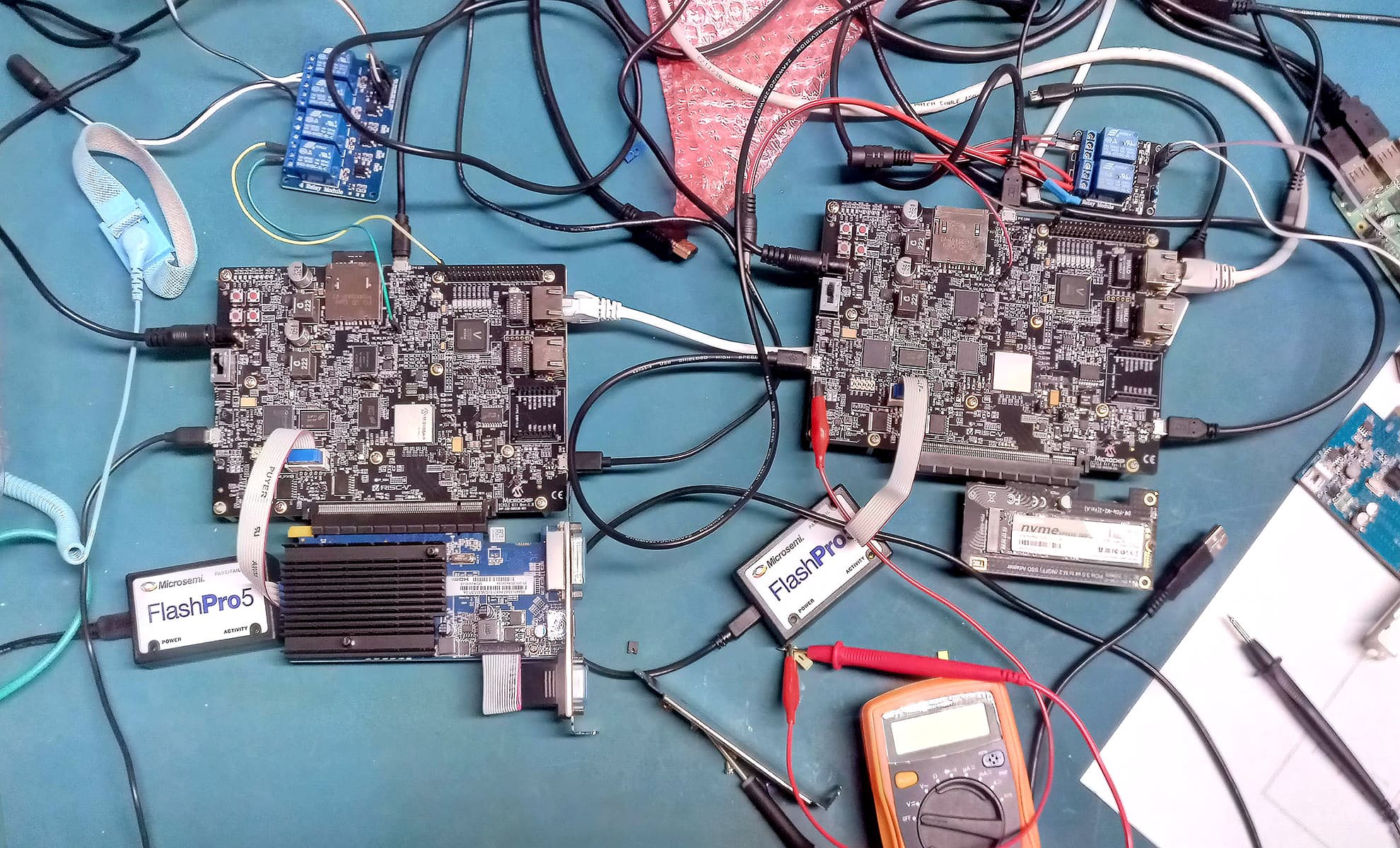

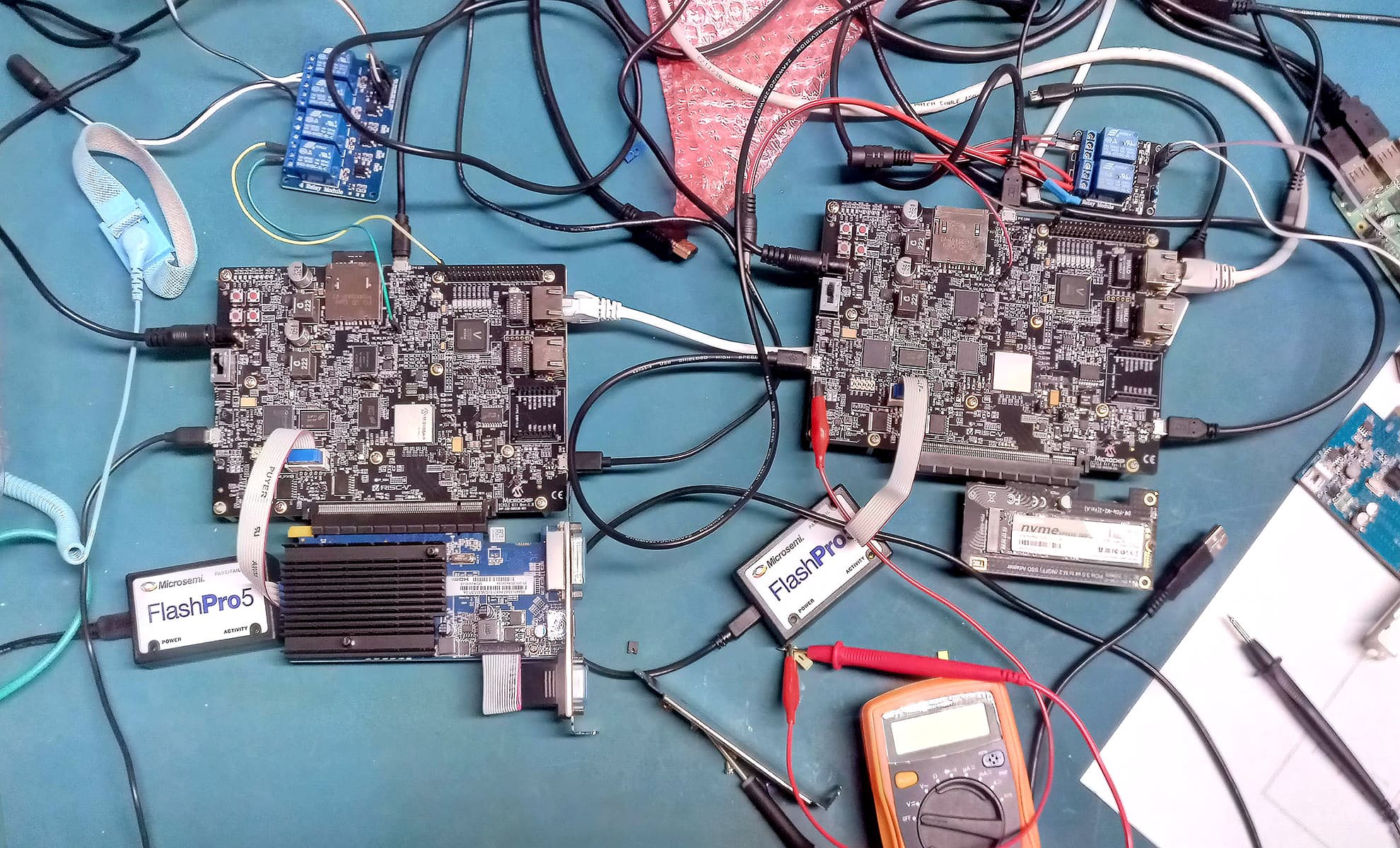

Continuing our work on robust testing in support of long-term maintainability, we present a testing pipeline that makes use of both LAVA and OpenQA to perform automated kernel tests on RISC-V hardware.

On one of our RISC-V projects, we were recently debugging a complex driver probing sequence in the U-Boot bootloader. Along the way we improved the debugging facilities available for U-Boot on RISC-V, specifically allowing developers and system integrators to see the callstack in the case that there is a crash during the early boot sequence.

A dive into our work to add further support for vector cryptography in RISC-V with QEMU!

Codethink is happy to sponsor GUADEC one year more

The problem with introducing these dependencies, is that part of your project now exists outside of your control.

We've ported GNOME OS to the PolarFire Icicle-Kit Devboard from Microchip.

Codethink continues to participate in the promising RISC-V ecosystem, and we have exciting news around Freedesktop SDK and GNOME.

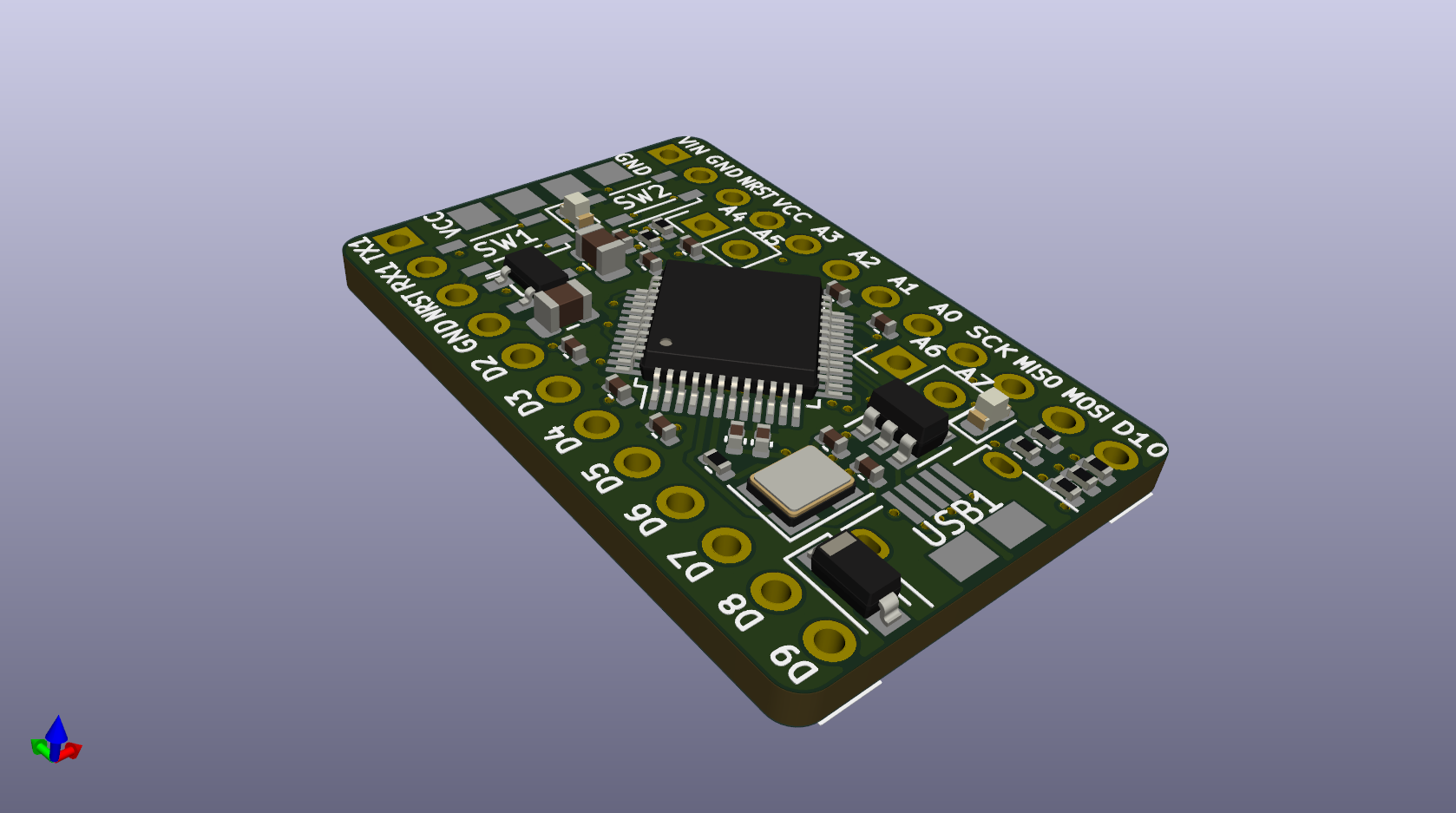

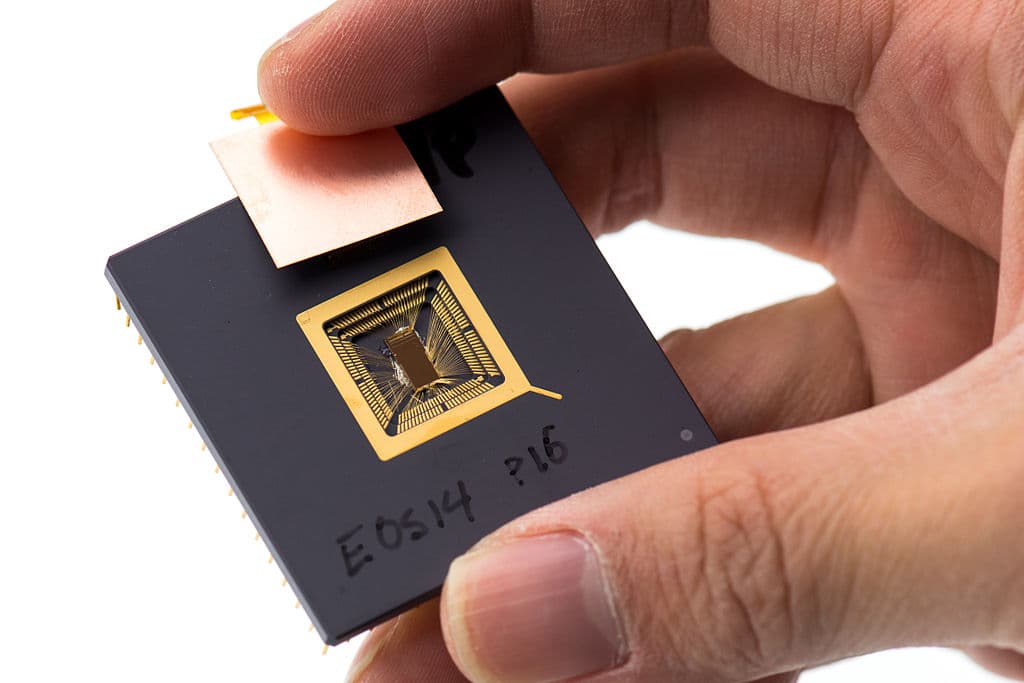

As part of Codethink's interest in RISC-V, we created some simple hardware.

As part of Codethink's interest in RISC-V I have been following the RISC-V kernel list. Whilst looking through the postings the following bug came up, titled: [syzbot] BUG: unable to handle kernel access to user memory in schedule_tail

When something as exciting as a completely open CPU architecture comes along, it's hard to stop Codethink's engineers from getting involved. We've set up an internal research project with the goal of learning about RISC-V, and we have some interesting results already.

Ben Dooks is our Senior Engineer and Open Source Consultant with more than 15 years’ experience contributing to Linux Kernel. Dooks joined Codethink 8 years ago, and since then he's been involved in a range of projects involving the Linux kernel, such as the MEG project, amongst others.

RISC-V is a new Instruction Set Architecture developed in the open and available for use without paying a license fee. This means there are no barriers to achieving open hardware implementations, which opens the door to performant (mostly) open hardware processors...

Tag Index

- Aarch64 (2)

- ABI Stability (1)

- AGL (1)

- Algorithm (2)

- Android Automotive (1)

- Ansible (1)

- API (1)

- Architecture (2)

- Arm (2)

- ASIL D (1)

- Atomic Upgrades (1)

- Audio (2)

- Automation (2)

- Automotive (13)

- Automotive Grade Linux (1)

- Autonomous Vehicle (1)

- Azure (2)

- Baserock (6)

- Bazel (5)

- Bazelize (2)

- Big-endian (1)

- Bloodlight (3)

- Board Support Packages (1)

- British Cycling (1)

- Bugs (1)

- Build (3)

- Build Engineering (16)

- Buildbarn (2)

- BuildBox (4)

- Buildfarm (1)

- BuildGrid (5)

- Buildroot (3)

- BuildStream (12)

- C (2)

- Case Design (1)

- CD (2)

- Certification (2)

- Christmas (2)

- CI (3)

- CICD (11)

- CIP (3)

- CLI (1)

- Cloud (1)

- Cloud-native (1)

- CMake (2)

- CNN (1)

- Code Review (1)

- Coding Puzzle (1)

- Community (6)

- Compilers (4)

- Conferences (14)

- Continuous Delivery (2)

- Continuous Integration (1)

- Coronavirus (4)

- Culture (11)

- CVE (1)

- Data (2)

- Databricks (1)

- DebConf (1)

- Debian (1)

- Debugging (4)

- Decision Analysis (1)

- Devices (1)

- DevOps (2)

- Distributed Builds (2)

- Diversity (2)

- Drivers (1)

- Eagle (1)

- ELCE (1)

- Electric vehicles (1)

- Electronics (2)

- Embedded (12)

- End-User Black-Box Testing (2)

- Erasure Codes (1)

- Error Correction (1)

- Events (13)

- Firmware (4)

- Flathub (1)

- Flatpak (3)

- FLOSS (1)

- Fortran (2)

- FOSDEM (9)

- FOSS (39)

- FOSS Backstage (1)

- FOSS Community (2)

- FPGA (2)

- Freedesktop SDK (5)

- GENIVI (3)

- Git (3)

- GitHub (1)

- Gitlab (1)

- GitOps (1)

- GNOME (19)

- GNOME OS (8)

- GStreamer (1)

- GUADEC (5)

- GUI (1)

- Hamsa (1)

- Hardware (10)

- Hardware Testing (2)

- Heart Monitor (1)

- Heart Rate Sensor (1)

- Hypervisors (1)

- Icicle (1)

- Icicle-Kit (1)

- IEC 61508 (1)

- Infrastructure (2)

- International Women's Day (2)

- Internet of Things (1)

- Internship (3)

- Interrogizer (2)

- Interview (8)

- ISO 26262 (1)

- ISO 9001 (1)

- IVI (1)

- Jetson (1)

- Jsonnet (1)

- Kernel (13)

- Kicad (2)

- Lava (1)

- libabigail (1)

- Linux (31)

- Linux Foundation (5)

- Linux Kernel (4)

- LLVM (1)

- Long Term Maintainability (27)

- Long Term Support (1)

- Lorry (4)

- Machine Learning (3)

- Mainline (2)

- Masterclass (1)

- Medical Devices (7)

- Meetup (2)

- MEG Project (1)

- Microcontroller (5)

- Mirroring (4)

- Mobile Devices (1)

- NVIDIA (3)

- Open Hardware (1)

- Open Source (73)

- Open Source Project (1)

- Open Source Summit (2)

- Open Source Summit Europe (1)

- openQA (5)

- OpenSCAD (1)

- OpenStack (3)

- Partnership (7)

- Performance (4)

- PinePhone (1)

- Podcast (1)

- Productivity (2)

- Programming (2)

- Project Manager (2)

- PyCon (1)

- Python (4)

- QEMU (11)

- QNX (1)

- R155/R156 (1)

- RAAPI (1)

- REAPI (2)

- RECC (1)

- Remote Asset (1)

- Remote Execution (5)

- Reproducibility (1)

- Research (2)

- RHEL (1)

- RISC-V (15)

- Robotics (1)

- Rust (6)

- Safety (19)

- Safety Engineering (1)

- Safety System (3)

- Schemas (2)

- Security (7)

- Server (1)

- SiFive (1)

- Software (4)

- Software Engineering (4)

- Software Test Libraries (1)

- STAMP (2)

- STM32 (2)

- STPA (8)

- systemd (6)

- Terraform (1)

- Testing (13)

- Teufel (2)

- Toolchain (3)

- Tracking (1)

- Troubleshooting (3)

- Trustable Software (14)

- TX2 (1)

- Upstream (6)

- USB (1)

- User Group (1)

- Validation (2)

- Visualisation (1)

- Women in Tech (3)

- XML (1)

- YAML (2)

- Yocto (1)

- YOLO (1)